# **UTC** UNISONIC TECHNOLOGIES CO., LTD

## MJE13005-H

## NPN SILICON POWER TRANSISTORS

## DESCRIPTION

These devices are designed for high-voltage, high-speed power switching inductive circuits where fall time is critical. They are particularly suited for 115 and 220 V SWITCHMODE.

## FEATURES

- \* V<sub>CEO(SUS)</sub>= 400 V

- \* Reverse bias SOA with inductive loads @  $T_C$  = 100°C

- \* Inductive switching matrix 2 to 4 Amp, 25 and 100°C

- t<sub>C</sub> @ 3A, 100°C is 180 ns (Typ)

- \* 700V blocking capability

- \* SOA and switching applications information

### APPLICATIONS

- \* Switching regulator's, inverters

- \* Motor controls

- \* Solenoid/Relay drivers

- \* Deflection circuits

## ORDERING INFORMATION

| Ordering Number                |                         | Deekege | Pin Assignment |   |   | Deaking  |

|--------------------------------|-------------------------|---------|----------------|---|---|----------|

| Lead Free                      | Halogen-Free            | Package | 1              | 2 | 3 | Packing  |

| MJE13005L-H-x-T92-B            | MJE13005G-H-x-T92-B     | TO-92   | В              | С | E | Tape Box |

| MJE13005-L-H-x-T92-K           | MJE13005G-H-x-T92-K     | TO-92   | В              | С | E | Bulk     |

| Note: Din assignment: E: Emitt | er B: Base C: Collector |         |                |   |   |          |

Note: Pin assignment: E: Emitter B: Base C: Collector

| MJE13005 <u>L</u> -H- <u>х-Т92-К</u><br>Т Т Т Т | (1)Packing Type  | (1) B: Tape Box, K: Bulk                        |

|-------------------------------------------------|------------------|-------------------------------------------------|

|                                                 | (2)Package ⊺ype  | (2) T92: TO-92                                  |

|                                                 | (3)Rank          | (3) x: refer to Classification of $h_{FE1}$     |

|                                                 | (4)Green Package | (4) L: Lead Free, G: Halogen Free and Lead Free |

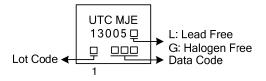

## MARKING

### ■ ABSOLUTE MAXIMUM RATINGS

| PARAMETER                                      |            | SYMBOL                            | RATINGS    | UNIT  |

|------------------------------------------------|------------|-----------------------------------|------------|-------|

| Collector-Emitter Voltage                      |            | V <sub>CEO(SUS)</sub>             | 400        | V     |

| Collector-Emitter Voltage (V <sub>BE</sub> =0) |            | V <sub>CES</sub>                  | 900        | V     |

| Collector-Base Voltage                         |            | V <sub>CBO</sub>                  | 900        | V     |

| Emitter Base Voltage                           |            | V <sub>EBO</sub>                  | 9          | V     |

| Collector Current                              | Continuous | Ι <sub>C</sub>                    | 4          | А     |

|                                                | Peak (1)   | I <sub>CM</sub>                   | 8          | А     |

| Base Current                                   | Continuous | Ι <sub>Β</sub>                    | 2          | А     |

|                                                | Peak (1)   | I <sub>BM</sub>                   | 4          | А     |

| Emitter Current                                | Continuous | Ι <sub>Ε</sub>                    | 6          | А     |

|                                                | Peak (1)   | I <sub>EM</sub>                   | 12         | Α     |

| Power Dissipation at T <sub>A</sub> =25°C      |            | P <sub>D</sub>                    | 0.8        | W     |

| Derate above 25°C                              |            |                                   | 6.4        | mW/°C |

| Operating and Storage Junction Temperature     |            | T <sub>J</sub> , T <sub>STG</sub> | -65 ~ +150 | °C    |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

### THERMAL DATA

| PARAMETER           | SYMBOL          | RATINGS | UNIT |

|---------------------|-----------------|---------|------|

| Junction to Ambient | θ <sub>JA</sub> | 150     | °C/W |

| Junction to Case    | θις             | 45      | °C/W |

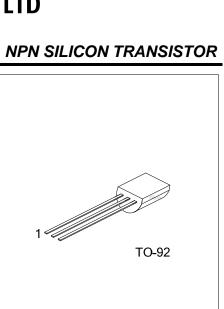

## NPN SILICON TRANSISTOR

1.7

0.4

4

0.9

μs

μs

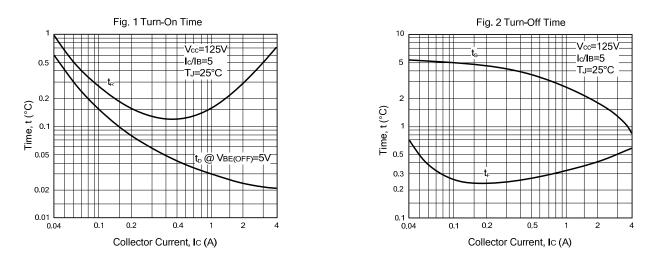

#### ELECTRICAL CHARACTERISTICS (Tc=25°C, unless otherwise specified) MAX UNIT SYMBOL MIN TYP PARAMETER **TEST CONDITIONS OFF CHARACTERISTICS** (Note 1) I<sub>C</sub>=10mA , I<sub>B</sub>=0 400 V Collector-Emitter Sustaining Voltage V<sub>CEO(SUS)</sub> V<sub>CBO</sub>=Rated Value, 1 V<sub>BE(OFF)</sub>=1.5V Collector Cutoff Current $I_{CBO}$ mΑ V<sub>CBO</sub>=Rated Value, 5 V<sub>BE(OFF)</sub>=1.5V, T<sub>C</sub>=100°C Emitter Cutoff Current V<sub>EB</sub>=9V, I<sub>C</sub>=0 $I_{EBO}$ 1 mΑ SECOND BREAKDOWN Second Breakdown Collector Current $I_{S/B}$ See Fig. 11 with bass forward biased Clamped Inductive SOA with Base RBSOA See Fig. 12 Reverse Biased **ON CHARACTERISTICS** (Note 1) $h_{FE1}$ I<sub>C</sub>=0.5A, V<sub>CE</sub>=5V 15 50 DC Current Gain I<sub>C</sub>=1A, V<sub>CE</sub>=5V 10 60 h<sub>FE2</sub> I<sub>C</sub>=2A, V<sub>CE</sub>=5V 8 40 $h_{\text{FE3}}$ I<sub>C</sub>=1A, I<sub>B</sub>=0.2A 0.5 V I<sub>C</sub>=2A, I<sub>B</sub>=0.5A 0.6 V Collector-Emitter Saturation Voltage V<sub>CE(SAT)</sub> V I<sub>C</sub>=4A, I<sub>B</sub>=1A 1 I<sub>C</sub>=2A, I<sub>B</sub>=0.5A, Ta=100°C 1 V V I<sub>C</sub>=1A, I<sub>B</sub>=0.2A 1.2 **Base-Emitter Saturation Voltage** VBE (SAT) I<sub>C</sub>=2A, I<sub>B</sub>=0.5A 1.6 V 1.5 I<sub>C</sub>=2A, I<sub>B</sub>=0.5A, T<sub>C</sub>=100°C V DYNAMIC CHARACTERISTICS Current-Gain-Bandwidth Product f⊤ I<sub>C</sub>=500mA, V<sub>CE</sub>=10V, f=1MHz MHz 4 **Output Capacitance** COB V<sub>CB</sub>=10V, I<sub>E</sub>=0, f=0.1MHz 65 pF SWITCHING CHARACTERISTICS Resistive Load (Table 1) 0.025 Delay Time t<sub>D</sub> 0.1 μs **Rise** Time V<sub>CC</sub>=125V, I<sub>C</sub>=2A, I<sub>B1</sub>=I<sub>B2</sub>=0.4A, 0.3 0.7 t<sub>R</sub> μs

Note: 1. Pulse Test: Pulse Width=5ms, Duty Cycle≤10%

2. Pulse Test: P<sub>W</sub>=300µs, Duty Cycle≤2%

#### CLASSIFICATION OF h<sub>FF1</sub>

| RANK  | А       | В       | С       | D       | E       |

|-------|---------|---------|---------|---------|---------|

| RANGE | 15 ~ 20 | 20 ~ 25 | 25 ~ 30 | 30 ~ 40 | 40 ~ 50 |

ts

t⊧

t<sub>P</sub>=25µs, Duty Cycle≤1%

Storage Time

Fall Time

## NPN SILICON TRANSISTOR

## APPLICATION INFORMATION

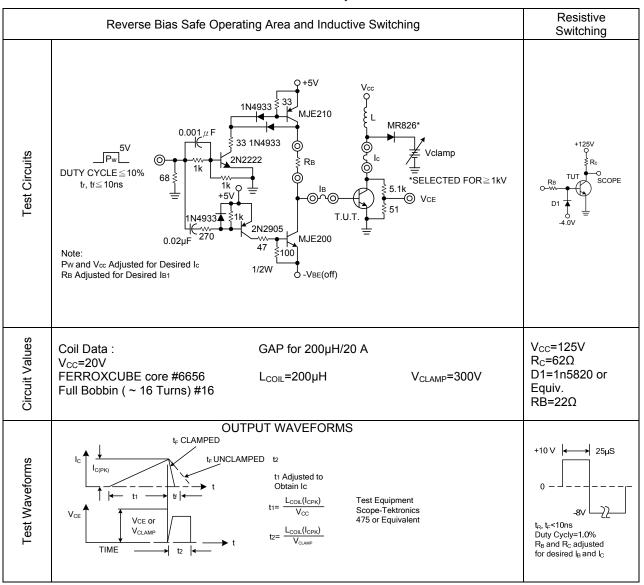

Table 1.Test Conditions for Dynamic Performance

## NPN SILICON TRANSISTOR

## RESISTIVE SWITCHING PERFORMANCE

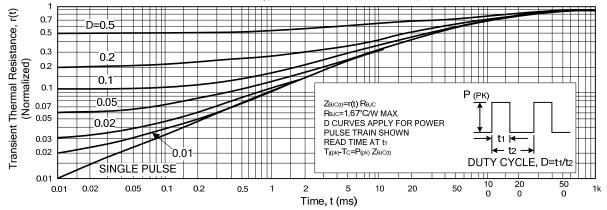

Fig. 3 Typical Thermal Response [ZeJC(t)]

## SAFE OPERATING AREA INFORMATION

### FORWARD BIAS

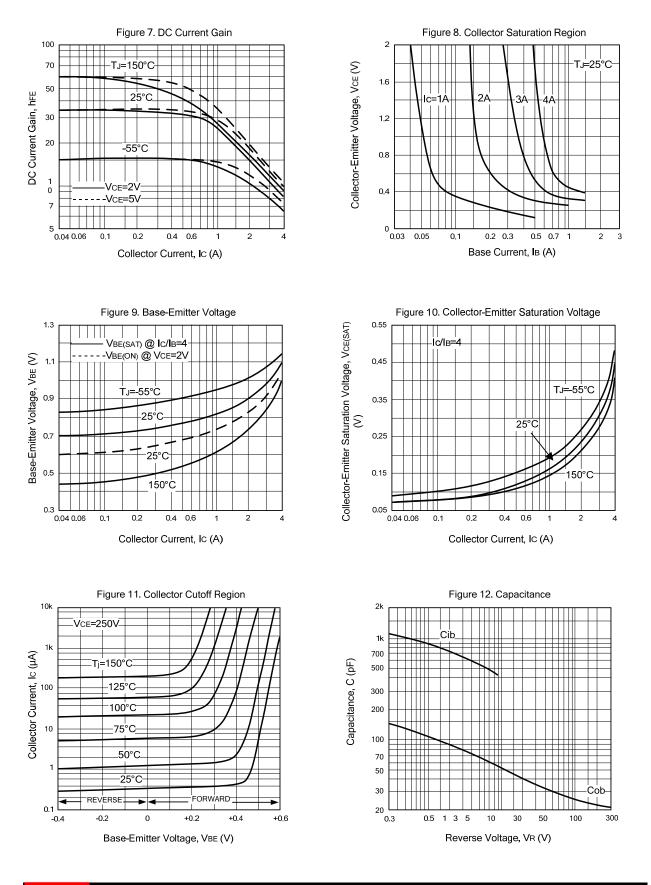

There are two limitations on the power handling ability of a transistor: average junction temperature and second breakdown. Safe operating area curves indicate  $I_{C}-V_{CE}$  limits of the transistor that must be observed for reliable operation; e., the transistor must not be subjected to greater dissipation than the curves indicate.

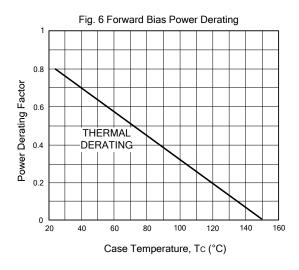

The data of Fig. 4 is based on  $T_C = 25^{\circ}C$ ;  $T_{J(PK)}$  is variable depending on power level. Second breakdown pulse limits are valid for duty cycles to 10% but must be derated when  $T_C \ge 25^{\circ}C$ . Second breakdown limitations do not derate the same as thermal limitations. Allowable current at the voltages shown on Fig. 4 may be found at any case temperature by using the appropriate curve on Fig. 6.

$T_{J(PK)}$  may be calculated from the data in Fig. 10. At high case temperatures, thermal limitations will reduce the power that can be handled to values less than the limitations imposed by second breakdown.

### **REVERSE BIAS**

For inductive loads, high voltage and high current must be sustained simultaneously during turn-off, in most cases, with the base to emitter junction reverse biased. Under these conditions the collector voltage must be held to a safe level at or below a specific value of collector current. This can be accomplished by several means such as active clamping, RC snubbing, load line shaping, etc. The safe level for these devices is specified as Reverse Bias Safe Operating Area and represents the voltage-current conditions during reverse biased turn-off. This rating is verified under clamped conditions so that the device is never subjected to an avalanche mode. Figure 5 gives the complete RBSOA characteristics.

## NPN SILICON TRANSISTOR

## TYPICAL CHARACTERISTICS

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.