# UNISONIC TECHNOLOGIES CO., LTD

L8200

**Preliminary**

LINEAR INTEGRATED CIRCUIT

# SINGLE LNB-BIAS, CONTROL AND POWER MANAGEMENT SOLUTION

#### DESCRIPTION

The UTC **L8200** is a single chip power management and control solution for LNB's. The highly integrated solution provides all the required FET and mixer bias, control detection and decoding, local oscillator switching and a stable power supply for the IF amplifier, and additional support functions. Packaged in a small 16 pin QFN package or 16 pin TSSOP package the UTC **L8200** only requires 3 external components providing a very small compact solution. Being at the heart of the LNB monitoring the control, power management and environmental conditions the UTC **L8200** is able to provide reliable solution eliminating effects such as false switching and over loading.

#### ■ FEATURES

- \* Single chip LNB bias, control and power management

- \* Integrated regulated supply for LNB

- \* Zero Gate FET switching

- \* Voltage detection for polarization switching

- \* 22kHz tone detector with signal rejection for band switching

- \* Programmable mixer and FET bias

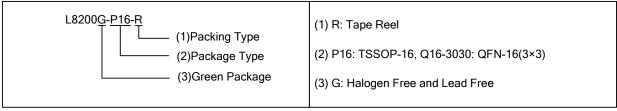

## ■ ORDERING INFORMATION

| Ordering Number   | Package     | Packing   |  |  |

|-------------------|-------------|-----------|--|--|

| L8200G-P16-R      | TSSOP-16    | Tape Reel |  |  |

| L8200G-Q16-3030-R | QFN-16(3×3) | Tape Reel |  |  |

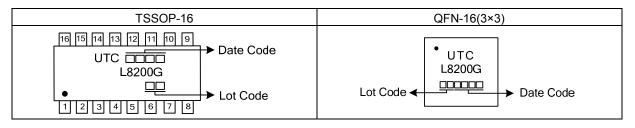

### ■ MARKING

www.unisonic.com.tw 1 of 6

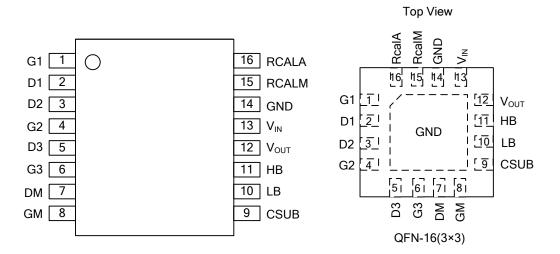

# **■ PIN CONFIGURATION**

# **■ PIN DESCRIPTION**

| Pin No.  |             | PIN NAME   | DESCRIPTION                                         |  |  |

|----------|-------------|------------|-----------------------------------------------------|--|--|

| TSSOP-16 | QFN-16(3×3) | FIN NAIVIE | DESCRIPTION                                         |  |  |

| 1        | 1           | G1         | To G of fet 1                                       |  |  |

| 2        | 2           | D1         | To D of fet 1                                       |  |  |

| 3        | 3           | D2         | To D of fet 2                                       |  |  |

| 4        | 4           | G2         | To G of fet 2                                       |  |  |

| 5        | 5           | D3         | To D of fet 3                                       |  |  |

| 6        | 6           | G3         | To G of fet 3                                       |  |  |

| 7        | 7           | DM         | To Drain of mix fet                                 |  |  |

| 8        | 8           | GM         | To Gate of mix fet                                  |  |  |

| 9        | 9           | CSUB       | connect an external cap to produce -2.5V            |  |  |

| 10       | 10          | LB         | To LB OSC.                                          |  |  |

| 11       | 11          | HB         | To HB OSC.                                          |  |  |

| 12       | 12          | $V_{OUT}$  | 5V voltage output terminal                          |  |  |

| 13       | 13          | $V_{IN}$   | Power supply (include both voltage and tone signal) |  |  |

| 14       | 14          | GND        | GND                                                 |  |  |

| 15       | 15          | RCALM      | Connect 22kohm to set Idm to 10mA                   |  |  |

| 16       | 16          | RCALA      | Connect 22kohm to set Id1, Id2, Id3 to 10mA         |  |  |

# ■ ABSOLUTE MAXIMUM RATING

| PARAMETER                   |             | SYMBOL           | RATINGS            | UNIT |

|-----------------------------|-------------|------------------|--------------------|------|

| Supply Voltage              |             | $V_{IN}$         | -0.6~25 continuous | V    |

| Supply Current              |             | I <sub>IN</sub>  | 120                | mA   |

| Davier Dissipation          | TSSOP-16    | Ъ                | 1.3                | W    |

| Power Dissipation           | QFN-16(3×3) | $P_D$            | 2                  | W    |

| Operating Temperature Range | )           | T <sub>OPR</sub> | -40~+85            | °C   |

| Storage Temperature Range   |             | T <sub>STG</sub> | -40~+150           | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

# **■ ELECTRICAL CHARACTERISTICS**

Measured at T<sub>A</sub>=25°C, V<sub>IN</sub>=13V, R<sub>CALA</sub>=R<sub>CALM</sub>=22kΩ(setting lds to 10 mA) unless otherwise specified.

| IVICUSUICU UL TA-20 O, VIN-10V, INCA | LA . TOALIN ==.  | ==\00tanig iao to 10 iii t/ aimooo                                    | <u> </u>         | ороонно |       |        |

|--------------------------------------|------------------|-----------------------------------------------------------------------|------------------|---------|-------|--------|

| PARAMETER                            | SYMBOL           | TEST CONDITIONS                                                       | IDITIONS MIN TYP |         | MAX   | UNIT   |

| Supply Voltage Operating Range       | V <sub>IN</sub>  |                                                                       | 8                |         | 22    | V      |

| Supply Current                       | _                |                                                                       |                  | -       | -     |        |

| No Load Supply Current (Note 1)      |                  | $I_{D1}=I_{D2}=I_{DM}=0$ mA                                           |                  | 2       | 3     | mA     |

| Max Total Load Current               |                  | QFN-16(3×3)                                                           |                  |         | 80    | mA     |

| Max Bias Load Current (Note 2)       | Icc              | I <sub>D1</sub> or I <sub>D2</sub> + I <sub>D3</sub> +I <sub>DM</sub> |                  |         | 40    | mA     |

| Max Osc Load Current (Note 2)        |                  | LB or HB                                                              |                  |         | 50    | mA     |

| Max Iout Load Current (Note 2)       |                  |                                                                       |                  |         | 50    | mA     |

| V <sub>OUT</sub>                     | V <sub>OUT</sub> | V <sub>IN</sub> =10.5V~21V, I <sub>OUT</sub> =30mA                    | 4.75             | 5       | 5.25  | V      |

| Substrate Voltage                    | $V_{SUB}$        | (Internally generated) I <sub>SUB</sub> =0mA                          | -3.0             | -2.5    | -2.0  | V      |

|                                      |                  | I <sub>SUB</sub> =-20uA                                               |                  |         | -2.0  | V      |

| V <sub>POL</sub> Threshold           | $V_{POL}$        | Applied via V <sub>IN</sub> pin                                       | 14.1             | 14.7    | 15.4  | V      |

| Pol Switching Speed                  | $T_{POL}$        | V <sub>IN Low</sub> =13V, V <sub>IN High</sub> =18V                   |                  |         | 1     | ms     |

| Output Noise                         |                  |                                                                       |                  |         |       |        |

| Drain Voltage                        |                  | $C_{GATE-GND}$ =4.7nF<br>$C_{DRAIN-GND}$ =10nF                        |                  |         | 0.02  | Vpk-pk |

| Gate Voltage                         |                  | IC <sub>GATE-GND</sub> =4.7nF<br>C <sub>DRAIN-GND</sub> =10nF         |                  |         | 0.005 | Vpk-pk |

| Tone Detector                        |                  | , =====================================                               | •                |         |       | •      |

| Tdetect Threshold                    | $V_{TONE}$       | Test Circuit 1                                                        | 100              | 170     | 300   | mV     |

| Rejection Freq (Note 3)              |                  | Test Circuit 1,<br>V(AC)I <sub>N</sub> =1Vp/p sq.w.                   | 1.0              | 7.5     |       | kHz    |

| LO Output Stage                      |                  |                                                                       |                  |         |       |        |

| LB V <sub>OUT</sub> Low              | .,               | II=0, Test Circuit 1<br>Tone enabled                                  | -0.05            | 0       | 0.05  | V      |

| LB V <sub>OUT</sub> High             | $V_{LB}$         | II=50mA, Test Circuit 1<br>Tone enabled                               | 4.5              | 5.0     | 5.25  | V      |

| HB V <sub>OUT</sub> Low              | .,,              | II=0, Test Circuit 1<br>Tone enabled                                  | -0.05            | 0       | 0.05  | V      |

| HB V <sub>OUT</sub> High             | $V_HB$           | II=50mA, Test Circuit 1<br>Tone enabled                               | 4.5              | 5.0     | 5.25  | V      |

# **■ ELECTRICAL CHARACTERISTICS (Cont.)**

| PARAMETER                                | SYMBOL             | BOL TEST CONDITIONS                                                                                                    |       | TYP  | MAX  | UNIT |  |

|------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|--|

| Gate Characteristics                     |                    |                                                                                                                        |       |      |      |      |  |

| G1 Output                                |                    |                                                                                                                        |       |      |      |      |  |

| Voltage Off                              | $V_{GIO}$          | I <sub>D1</sub> =0, V <sub>IN</sub> =14V, I <sub>G1</sub> =0                                                           | -0.05 | 0    | 0.05 | V    |  |

| Voltage Low                              | V <sub>GIL</sub>   | V <sub>IN</sub> =15.5V, I <sub>D1</sub> ≤12mA,<br>I <sub>G1</sub> =-10uA                                               | -3.0  | -2.5 | -2.0 | ٧    |  |

| Voltage High                             | $V_{GIH}$          | V <sub>IN</sub> =15.5V, I <sub>D1</sub> ≥8mA, I <sub>G1</sub> =0                                                       | 0.4   | 0.65 | 1.0  | V    |  |

| G2 Output                                |                    |                                                                                                                        |       |      |      |      |  |

| Voltage Off                              | $V_{G2O}$          | V <sub>IN</sub> =15.5V, I <sub>D2</sub> =0, I <sub>G2</sub> =0                                                         | -0.05 | 0    | 0.05 | V    |  |

| Voltage Low                              | $V_{\rm G2L}$      | V <sub>IN</sub> =14V, I <sub>D2</sub> ≤12mA,<br>I <sub>G2</sub> =-10uA                                                 | -3.0  | -2.5 | -2.0 | V    |  |

| Voltage High                             | $V_{\rm G2H}$      | V <sub>IN</sub> =14V, I <sub>D2</sub> ≥8mA, I <sub>G2</sub> =0                                                         | 0.4   | 0.65 | 1.0  | V    |  |

| G3 Output                                |                    |                                                                                                                        |       |      |      |      |  |

| Voltage Low                              | $V_{G3L}$          | I <sub>D3</sub> /m≤12mA, I <sub>G3</sub> /m=-10uA                                                                      | -3.0  | -2.5 | -2.0 | V    |  |

| Voltage High                             | $V_{\rm G3H}$      | I <sub>D3</sub> /m≥8mA,I <sub>G3</sub> /m=0                                                                            | 0.4   | 0.5  | 1.0  | V    |  |

| Drain Characteristics                    |                    |                                                                                                                        |       |      |      |      |  |

| D1 Output                                |                    |                                                                                                                        |       |      |      |      |  |

| Voltage High                             | $V_{D1}$           | V <sub>IN</sub> =15.5V, I <sub>D1</sub> =10mA                                                                          | 1.8   | 2.0  | 2.2  | V    |  |

| Leakage Current                          | I <sub>LEAK1</sub> | V <sub>IN</sub> =14V, V <sub>D1</sub> =0.5                                                                             |       |      | 10   | uA   |  |

| D2 Output                                |                    |                                                                                                                        | _     | _    | _    |      |  |

| Voltage High                             | $V_{D2}$           | V <sub>IN</sub> =14V, I <sub>D2</sub> =10mA                                                                            | 1.8   | 2.0  | 2.2  | V    |  |

| Leakage Current                          | I <sub>LEAK2</sub> | V <sub>IN</sub> =15.5V, V <sub>D2</sub> =0.5                                                                           |       |      | 10   | uA   |  |

| D3 Output                                |                    |                                                                                                                        |       |      |      |      |  |

| Voltage High                             | V <sub>D3</sub>    | V <sub>IN</sub> =15.5V, I <sub>D3</sub> =10mA                                                                          | 1.8   | 2.0  | 2.2  | V    |  |

| Dm Output                                |                    |                                                                                                                        |       |      |      |      |  |

| Voltage High                             | $V_{DM}$           | I <sub>DM</sub> =10mA                                                                                                  | 0.5   | 0.6  | 0.7  | V    |  |

| D1, 2, 3 and M                           |                    |                                                                                                                        |       |      |      |      |  |

| Delta V <sub>D</sub> vs. V <sub>IN</sub> | $\Delta V_{DV}$    | V <sub>IN</sub> =9~21V                                                                                                 |       | 0.5  |      | %/V  |  |

| Delta V <sub>D</sub> vs. T <sub>J</sub>  | $\Delta V_{DT}$    | T <sub>J</sub> = -40 ~ +85°C                                                                                           |       | 50   |      | ppm  |  |

| FET Current Range                        |                    | I <sub>D1</sub> , I <sub>D2</sub> & I <sub>D3</sub>                                                                    | 0     |      | 15   | mA   |  |

| Mixer Current Range                      |                    | I <sub>DM</sub>                                                                                                        | 0     |      | 10   | mA   |  |

| Drain Current                            | I <sub>D</sub>     | I <sub>D1</sub> , I <sub>D2</sub> , I <sub>D3</sub> & I <sub>DM</sub> ,<br>R <sub>CALA</sub> & R <sub>CALM</sub> =22kΩ | 8     | 10   | 12   | mA   |  |

| Delta I <sub>D</sub> vs. V <sub>CC</sub> | $\Delta I_{DV}$    | V <sub>CC</sub> =9~21V                                                                                                 |       | 0.5  |      | %/V  |  |

| Delta I <sub>D</sub> vs. T <sub>J</sub>  | $\Delta I_{DT}$    | T <sub>J</sub> =-40~+85°C                                                                                              |       | 0.05 |      | %/°C |  |

| Notes: 1 Those parameters are rela       |                    | Line                                                                                                                   | •     | •    | •    |      |  |

Notes: 1. These parameters are related to  $R_{\text{CAL}}$  values.

<sup>2.</sup> The total combined load currents should not exceed the stated maximum load current.

<sup>3.</sup> The UTC **L8200** series will also reject DiSEqC and other common switching tone bursts.

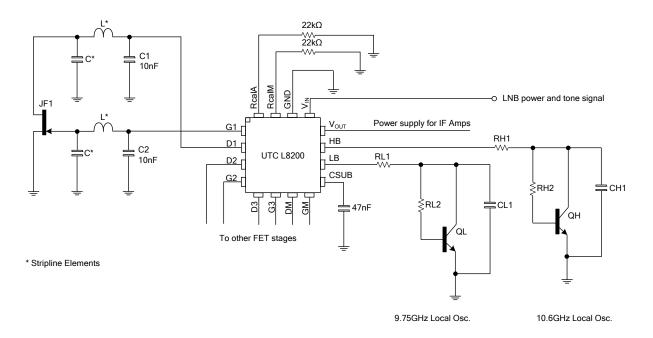

#### ■ TYPICAL APPLICATION CIRCUIT

Capacitors C1 and C2 ensure that residual power supply and substrate generator noise is not allowed to affect other external circuits which may be sensitive to RF interference. They also serve to suppress any potential RF feed through between stages via the UTC L8200. These capacitors are required for all stages used. Values of 10nF and 4.7nF respectively are recommended however this is design dependent and any value between 1nF and 100nF could be used. The capacitor CSUB is an integral part of the UTC L8200 's negative supply generator. The negative bias voltage is generated on-chip using an internal oscillator. The required value of capacitor CSUB is 47nF. This generator produces a low current supply of approximately -3V. Although this generator is intended purely to bias the external FETs, it can be used to power other external low current circuits via the CSUB pin. Resistor R<sub>CALA</sub> sets the drain current at which all external amplifier FETs are operated and R<sub>CALM</sub> sets the mixer bias current. If any bias control circuit is not required, its related drain and gate connections may be left open circuit without affecting the operation of the remaining bias circuits. The UTC L8200 have been designed to protect the external FETs form adverse operating conditions. With a JFET connected to any bias circuit, the gate output voltage of the bias circuit can not exceed the range -3.0V~1V under any conditions, including power up and power down transients. Should the negative bias generator be shorted or overloaded so that the drain current of the external FETs can no longer be controlled, the drain supply to FETs is shut down to avoid damage to the FETs by excessive drain current. UTC L8200 incorporates over and under voltage protection so is the receiver or installation develops a fault the LNB will shut down and restart once operating conditions are back to normal.

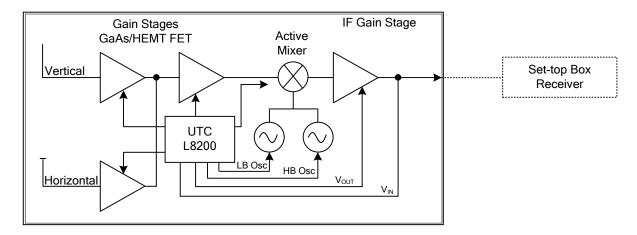

#### SINGLE UNIVERSAL BLOCK DIAGRAM

The following block diagram below shows the main elements of a single universal LNB. A single chip solution provides all the FET and mixer bias, control signal detect for polarization and band selection and all the necessary power management functions required within a single universal LNB.

Polarization and band switching on the UTC **L8200** uses the standard 13~17V and 22kHz as defined by Astra. The exception is that the devices voltage detector has a much tighter tolerance than required to increase field reliability.

The single  $V_{IN}$  pin is used internally for three functions, LNB and IC power supply, voltage detection and tone detection. The IC's is self powering via an internal regulator which utilizes the 13~17V control voltage from the satellite receiver. The regulated voltage is used to supply the IC and is also outputted to the  $V_{OUT}$  pin to provide the power supply for the remaining element of the LNB such as the IF amplifiers. The 13~17V from the receiver is feed via a tight tolerance voltage detector with integrated filtering which removes unwanted signals or interference. The results from the detectors output enables one of 2 bias circuits to turn one of either Fet1 or FET2 on. The internal tone detector allows the device to detect the 22kHz tone which is superimposed on the LNB power line (13~17V signal), this is achieved with no external filtering components. The tone detector rejects all unwanted signals including transients from other parts of the LNB system. The tone detector controls a drive circuits which powers and one of two oscillators, normally used to switch between low and high band in universal applications. The functional table below shows the operation of the FET and Mixer bias, oscillator output and the LNB power supply.

#### **■ FUNCTION TABLE**

| INP                 | UTS       |          | _        | _      | OUTPUTS |       | _     |                      |

|---------------------|-----------|----------|----------|--------|---------|-------|-------|----------------------|

| V <sub>IN</sub> (V) | FIN (kHZ) | FET1     | FET2     | FET3   | MIXER   | LB(V) | HB(V) | V <sub>OUT</sub> (V) |

| <14.1               | 0         | Disabled | Active   | Active | Active  | 5.0   | 0     | 5.0                  |

| >15.4               | 0         | Active   | Disabled | Active | Active  | 5.0   |       | 5.0                  |

| <14.1               | 22        | Disabled | Active   | Active | Active  | 0     | 5.0   | 5.0                  |

| >15.4               | 22        | Active   | Disabled | Active | Active  | 0     | 5.0   | 5.0                  |

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.