L11815B Preliminary CMOS IC

# 1.5A CMOS LDO

### **■** DESCRIPTION

The UTC **L11815B** is a positive, linear regulator. One of its features is the very low quiescent current typically as low as  $45\mu A$  and the dropout voltage is extremely low.

The internal circuit includes thermal shutdown and current fold-back mechanism to prevent device failure when the circuit is operated in the bad conditions.

In application, the UTC **L11815B** needs a low noise and regulated supply. For stability, the output capacitance value should be  $4.7\mu F$  or more.

The UTC **L11815B** is an ideal for battery applications, such as instrumentations, portable electronics, wireless devices, cordless phones, PC peripherals, and battery powered widgets. The output voltage values are set during manufacturing and their accuracy is trimmed to within 1.5%.

### **■ FEATURES**

- \* Quiescent Current (45µA typ.)

- \* Accurate : ±1.5%

- \* Very Low Dropout Voltage

- \* Guaranteed 1.5A Output

- \* Over-Temperature Shutdown

- \* With Current Limiting

- \* Short Circuit Current Fold-Back

- \* Power-Saving Shutdown Mode

- \* Low Temperature Coefficient

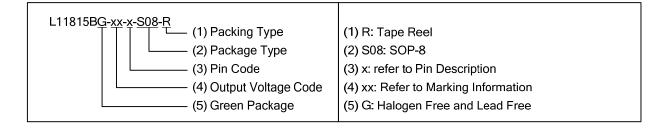

## **■ ORDERING INFORMATION**

| Ordering Number     | Package | Packing   |  |

|---------------------|---------|-----------|--|

| L11815BG-xx-x-S08-R | SOP-8   | Tape Reel |  |

<u>www.unisonic.com.tw</u> 1 of 6

## MARKING INFORMATION

| PACKAGE | VOLTAGE CODE | MARKING                                                  |

|---------|--------------|----------------------------------------------------------|

| SOP-8   | AD: ADJ      | 8 7 6 5 UTC DDD Date Code L11815BG Voltage Code L1 2 3 4 |

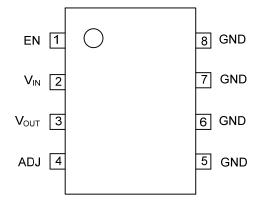

## **■ PIN CONFIGURATION**

## **■ PIN DESCRIPTION**

| PIN NO | PIN NAME         | Pin Code | DESCRIPTION                                                                                                       |

|--------|------------------|----------|-------------------------------------------------------------------------------------------------------------------|

| 1      | EN               |          | Enable pin. When pulled low, the PMOS pass transistor turns off, current consuming less than 1μA.                 |

| 2      | V <sub>IN</sub>  |          | Input voltage pin. It should be decoupled with 1µF or greater capacitor.                                          |

| 3      | V <sub>OUT</sub> | С        | LDO voltage regulator output pin. It should be decoupled with a 4.7µF or greater value low ESR ceramic capacitor. |

| 4      | ADJ              |          | Feedback output voltage for adjustable device.                                                                    |

| 5~8    | GND              |          | Ground connection pin.                                                                                            |

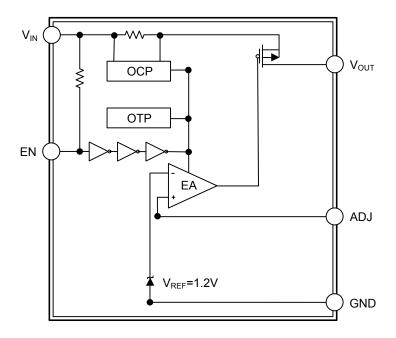

## ■ BLOCK DIAGRAM

### ■ ABSOLUTE MAXIMUM RATING

| PARAMETER             | SYMBOL           | RATINGS                  | UNIT |

|-----------------------|------------------|--------------------------|------|

| Input Voltage         | $V_{IN}$         | -0.3 ~ +8                | V    |

| Input Voltage (EN)    | $V_{EN}$         | -0.3 ~ +8                | V    |

| Output Voltage        | $V_{OUT}$        | $-0.3 \sim V_{IN} + 0.3$ | V    |

| Output Current        | I <sub>OUT</sub> | PD<br>VIN - VOUT         | mA   |

| Power Dissipation     | $P_{D}$          | 810                      | mW   |

| Junction Temperature  | $T_J$            | 150                      | °C   |

| Operating Temperature | $T_{OPR}$        | -40~+85                  | °C   |

| Storage Temperature   | T <sub>STG</sub> | -65~+150                 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

### ■ THERMAL DATA

| PARAMETER               | SYMBOL        | RATINGS | UNIT |

|-------------------------|---------------|---------|------|

| Junction to Ambient     | $\theta_{JA}$ | 150     | °C/W |

| Junction to Case (Note) | θις           | 60      | °C/W |

Note:  $\,\,\theta_{\text{JC}}$  on center of molding compound if IC has on tab.

## ■ ELECTRICAL CHARACTERISTICS (V<sub>IN</sub> =V<sub>OUT</sub>+2V, V<sub>EN</sub> =V<sub>IN</sub>, Ta =25°C, unless otherwise specified)

| PARAMETER                                 | SYMBOL                           | TEST CONDITIONS                                                                   |                               |       | TYP  | MAX             | UNIT   |

|-------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------|-------------------------------|-------|------|-----------------|--------|

| Input Voltage                             | $V_{IN}$                         |                                                                                   |                               | Note1 |      | 7               | V      |

| Output Voltage Accuracy                   | $V_{OUT}$                        | $V_{EN} = V_{EH(MIN)}, I_{OUT} = 1mA$                                             |                               | -1.5  |      | 1.5             | %      |

| ADJ Reference Voltage                     | $V_{REF}$                        |                                                                                   |                               | 1.176 | 1.2  | 1.224           | V      |

|                                           |                                  | 1 4 4                                                                             | V <sub>OUT</sub> <2.0V        | -0.15 |      | 0.15            | %      |

| Line Regulation                           | <u>Δ</u> Vουτ<br><b>V</b> ουτ    | I <sub>OUT</sub> =1mA<br>V <sub>IN</sub> =V <sub>OUT</sub> +1~V <sub>OUT</sub> +2 | 4.0 >V <sub>OUT</sub> ≥2.0V   | -0.1  | 0.02 | 0.1             | %      |

|                                           | <b>V</b> 001                     | VIN-VOUT+1~VOUT+2                                                                 | 4.0V≤V <sub>OUT</sub>         | -0.4  |      | 0.4             | %      |

| Load Regulation                           | $\frac{\Delta V_{OUT}}{V_{OUT}}$ | I <sub>OUT</sub> =1mA ~ 1.5A                                                      |                               | -1    | 0.2  | 1               | %      |

| Output Current                            | l <sub>out</sub>                 | V <sub>OUT</sub> >1.2V                                                            |                               | 1500  |      |                 | mA     |

| Current Limit                             | I <sub>LIM</sub>                 | V <sub>OUT</sub> >1.2V                                                            |                               | 1500  | 2000 |                 | mA     |

| Short Circuit Current                     | I <sub>SC</sub>                  | V <sub>OUT</sub> <0.4V                                                            |                               |       | 750  |                 | mA     |

| Minimum Load Current                      | I <sub>MIN</sub>                 |                                                                                   |                               | 1     |      |                 | mA     |

| Ground Pin Current                        | $I_{GND}$                        | I <sub>OUT</sub> =1mA ~ 1.5A                                                      |                               |       | 45   |                 | μΑ     |

| ADJ Input Bias Current                    | $I_{ADJ}$                        | $V_{IN} = 5V$ , $V_{ADJ} = 1.24$                                                  | 2V                            |       | 1    |                 | μΑ     |

|                                           | $V_{D}$                          | 1 454                                                                             | 1.5V <v<sub>OUT≤2.0V</v<sub>  |       |      | 1300            | mV     |

| Dropout Voltage                           |                                  | I <sub>OUT</sub> =1.5A,<br>V <sub>OUT</sub> =V <sub>OUT</sub> -2.0%               | 2.0V <v<sub>OUT ≤2.8V</v<sub> |       |      | 800             | mV     |

|                                           |                                  | VOUT-VOUT -2.076                                                                  | 2.8V <v<sub>OUT</v<sub>       |       |      | 600             | mV     |

| Over Temperature Shutdown                 | OTS                              |                                                                                   |                               |       | 150  |                 | °C     |

| Over Temperature Hysteresis               | OTH                              |                                                                                   |                               |       | 30   |                 | °C     |

| Temperature Coefficient of Output Voltage | $T_{C}V_{O}$                     |                                                                                   |                               |       | 30   |                 | ppm/°C |

| Barrier Caralla Britantia                 | PSRR                             | I <sub>O</sub> =100mA,                                                            | f=1kHz                        |       | 50   |                 | dB     |

| Power Supply Rejection                    |                                  | C <sub>O</sub> =4.7µF ceramic                                                     | f=10kHz                       |       | 20   |                 | dB     |

| Output Voltage Noise                      | eN                               | f=10Hz~100kHz, I <sub>OUT</sub> =10mA, C <sub>O</sub> =4.7µF                      |                               |       | 30   |                 | μVrms  |

| ENI locate Through and                    | $V_{EH}$                         |                                                                                   |                               | 2.0   |      | V <sub>IN</sub> | V      |

| EN Input Threshold                        | V <sub>EL</sub>                  |                                                                                   |                               | 0     |      | 0.4             | V      |

| EN Input Bias Current                     | I <sub>EH</sub>                  | V <sub>IN</sub> = 7V                                                              |                               |       |      | 0.1             | μA     |

|                                           | I <sub>EL</sub>                  | V <sub>EN</sub> =0V, V <sub>IN</sub> = 7V                                         |                               |       |      | 0.5             | μA     |

| Shutdown Supply Current                   | I <sub>SD</sub>                  | $V_{IN} = 5V$ , $V_{O} = 0V$ , $V_{EN} = 0V$                                      |                               |       | 0.5  | 2               | μA     |

Note:  $V_{IN(MIN)} = V_{OUT} + V_{DROPOUT}$

#### DETAILED DESCRIPTION

The UTC **L11815B** of CMOS regulators insist of a PMOS pass transistor, voltage reference, error amplifier, over-current protection, and thermal shutdown.

The error amplifier, over-current shutdown, and thermal protection circuits provides data for P-channel pass transistor. The error amplifier takes output voltage for a precision reference in the normal operation and the normal operation is restored when the junction temperature drops below 120°C. Over-current and Thermal shutdown circuits start to work when the junction temperature is higher than 140°C, or the current is higher than 2.2A. The output voltage stays low when the thermal shutdown is in active.

The UTC **L11815B** behaves like a current source when the load reaches 2.2A. But the current would fall back to 600mA to prevent excessive power loss when the load impedance value is below  $0.3\Omega$ . Normal operation is restored when the load resistance value is higher than  $0.75\Omega$ .

#### **■ EXTERNAL CAPACITORS**

The UTC **L11815B** has an output capacitor to ground of  $4.7\mu\text{F}$  or more in the stable operation. Ceramic capacitors can provide the lowest ESR with the best AC performance. Aluminum Electrolytic capacitors, in contrast, have the highest ESR with poorest AC response. Unfortunately, large value ceramic capacitors are comparatively expensive. So we can parallel a  $0.1\mu\text{F}$  ceramic capacitor with a  $10\mu\text{F}$  Aluminum Electrolytic. The result is low ESR, high capacitance, and low overall cost.

A second capacitor is recommended between the input and ground to stabilize input voltage. To get an ideal effect the value of the input capacitor should be at least 0.1µF.

A third capacitor can be connected between the bypass pin and ground. This capacitor can be a low cost Polyester Film varies in the range of  $0.001 \sim 0.01 \mu F$ . A larger capacitor improves the AC ripple rejection, but also makes the output come up slowly. This "Soft" turn-on is desirable in some applications to limit turn-on surges.

At last, all the capacitors should keep a close proximity to the pins; you can achieve this with a star connection.

### ■ ENABLE

When pulled low, the PMOS pass transistor shuts off, and all internal circuits are powered down. In this state, the quiescent current is less than 1µA. This pin behaves much like an electronic switch.

$100k\Omega$  resistor is necessary between  $V_{EN}$  source and EN pin when  $V_{EN}$  is higher than  $V_{IN}$ .

(Note: There is no internal pull-up for EN PIN.)

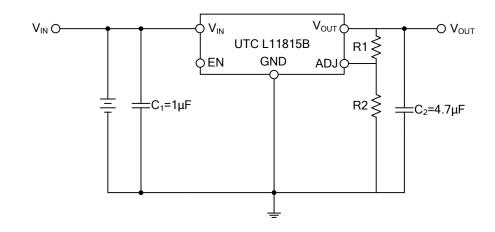

#### ADJUSTABLE VERSION

The adjustable version uses external feedback resistors to generate an output voltage anywhere from 1.5V to 5.0V.  $V_{ADJ}$  is trimmed to 1.2V and  $V_{OUT}$  is given by the equation:

$V_{OUT} = V_{ADJ} (1 + R1 / R2)$

Feedback resistors R1 and R2 should be high enough to keep quiescent current low, but increasing R1 + R2 will reduce stability. In general, R1 and R2 in the 10's of  $k\Omega$  will produce adequate stability, given reasonable layout precautions. To improve stability characteristics, keep parasitics on the ADJ pin to a minimum, and lower R1 and R2 values.

### ■ TYPICAL APPLICATION CIRCUIT

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.